Полный список команд

Ниже приводится полный список команд устройства умножителя-накопителя MAC, также в соответствии с принятыми ранее условными сокращениями. Назначение команд приводится в тексте описания этих команд и комментариях для некоторых из команд.

Команды умножения:

[IF cond] |MR| = xop * |yop| |(SS) |;

|MF| |xop| |(SU) |

|(US) |

|(UU) |

|(RND)|

Здесь присутствуют новые символы, которые имеют следующее назначение:

S - входной операнд xop или yop знаковый;

U - входной операнд xop или yop беззнаковый;

RND - выходное значение округляется.

Например, команда:

MR=MX0*MY0(SU);

означает, что в регистр MR будет занесен результат умножения знакового значения из регистра MX0 на беззнаковое значение из регистра MY0.

Команда:

MR=SR1 *MY0(RND);

означает, что в регистр MR будет занесен результат умножения значения из регистра SR1 на значение из регистра MY0 и результат вычисления будет округлен.

Команды умножения с накоплением:

[IF cond] |MR| = MR + xop * |yop| |(SS) |;

|MF| |xop| |(SU) |

|(US) |

|(UU) |

|(RND)|

Пример:

MR=MR+MX0*MY0 (SS);

Здесь в регистр MR будет занесен результат сложения предыдущего значения регистра MR с результатом умножения знакового значения из регистра MX0 на знаковое значение из регистра MY0.

Команды умножения с вычитанием:

[IF cond] |MR| = MR - xop * |yop| |(SS) |;

|MF| |xop| |(SU) |

|(US) |

|(UU) |

|(RND)|

Команды пересылки MR:

[IF cond] |MR| = MR |(RND)|;

|MF|

Фактически эти команды осуществляют пересылку содержимого регистра MR в регистр MR или в регистр MF с округлением значения.

Команды очистки:

[IF cond] |MR| = 0;

|MF|

Команда условного насыщения регистра MR:

IF MV SAT MR;

Здесь MV - код условия переполнения умножителя.

Для всех команд MAC разрешено использовать следующие операнды:

xop: MX0, МХ1, AR, MR0, MR1, MR2, SR0, SR1;

yop: MY0, MY1, MF;

Коды условия IF соответствуют кодам, приведенным ранее в табличном виде.

Примеры записи команд:

MR=MR+MX0*MY0(SS); /* Присвоить регистру MR значение суммы регистров MR и

произведения MX0 на MY0, где оба операнда произведения знаковые*/

MF=AR*MY0(RND) /* Присвоить регистру MF значение произведения регистра AR на

MY0, с округлением результата*/

MF=AR*MY0(RND), MY1=DM(I3,M3); /* Мультипроцессорная команда вычисления

произведения и одновременной пересылки данных из памяти в регистр*/

MF=MR(RND); /* Осуществить пересылку содержимого регистра MR в регистр MF с

округлением значения */

IF EQ MR=0; /* Очистить регистр MR, если предыдущий результат равен нулю */

Глава 16. Устройство сдвига

В этой главе говорится об устройстве сдвига сигнального процессора и выполняемых с его помощью командах.

Устройство сдвига именуется как Shifter и обеспечивает полный набор сдвиговых функций для 16-разрядных операндов, результатом которых является 32-разрядное слово данных. К числу сдвиговых функций относятся арифметические сдвиги, логические сдвиги и нормализация. Кроме того, shifter позволяет вычислить порядок (экспоненту) числа и порядок для целого массива (блока) чисел. Эти базовые функции могут быть объединены для быстрого преобразования любого формата чисел, в том числе и чисел с плавающей точкой.

Структура устройства сдвига

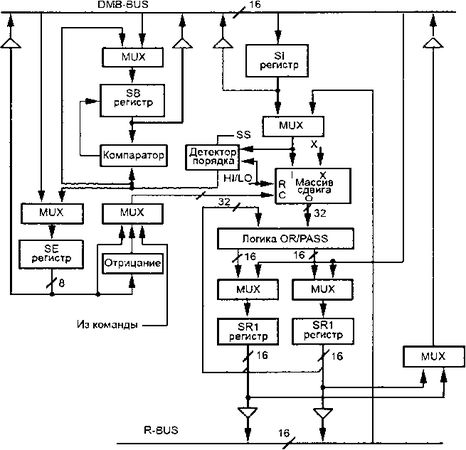

На рис. 16.1 представлена структурная схема устройства сдвига. Shifter включает в себя следующие основные блоки: массив сдвига, логику OR/PASS (ИЛИ/ПЕРЕДАЧА), детектор порядка и логику сравнения порядка.

Рис. 16.1. Структурная схема устройства сдвига

Массив сдвига состоит из шестнадцати 32-разрядных регистров. Он принимает 16-разрядные данные и в одном цикле может поместить их в любой позиции 32-разрядного поля вывода, начиная с данных, полностью сдвинутых влево, и кончая данными, полностью сдвинутыми вправо, за один цикл. Это дает 49 вариантов возможных размещений 16-разрядных входных данных в 32- разрядном поле вывода, как показано в табл. 16.1.

Таблица 16.1 Варианты возможных размещений 16-разрядных входных данных в 32-разрядном поле вывода

| N | Разряды | |||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 1 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 2 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 15 |

| 3 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 15 | 14 |

| … | ||||||||||||||||||||||||||||||||

| 17 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 18 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | X |

| … | ||||||||||||||||||||||||||||||||

| 33 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 34 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| … | ||||||||||||||||||||||||||||||||

| 47 | 1 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 48 | 0 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X |

| 49 | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | X | Z | X | X | X |

Размещение 16 входных разрядов определяется кодом управления "С" и сигналом ссылки HI/LO. Код управления "С" является 8-битным значением, которое указывает направление сдвига и число разрядов, на которое необходимо будет сдвинуть данные.