Операции MAC

Теперь рассмотрим операции вычислительного устройства MAC, входные форматы данных, обработку переполнения и насыщения.

Набор стандартных операций MAC приведен в табл. 15.2.

Таблица 15.2 Набор стандартных операций MAC

| Операция | Назначение |

|---|---|

| X*Y | Умножение X на Y |

| MR+X*Y | Умножение X на Y и сложение с MR |

| MR-X*Y | Умножение X на Y и вычитание из MR |

| 0 | Очистка MR |

Как было сказано выше, сигнальный процессор ADSP-2181 обеспечивает два режима работы операций умножения с накоплением. Первый из них - режим работы с дробными числами в формате 1.15. Второй - режим работы с целыми числами в формате 16.0.

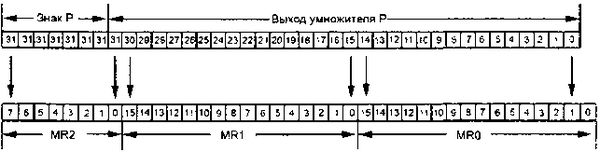

В дробном режиме выходной регистр P корректирует формат, т.е. прежде чем добавить значение в MR, оно сдвигается на один разряд влево. Таким образом, бит 31 регистра P запишется в 32-й разряд регистра MR, а 0-й разряд - в первый. В позицию младшего разряда (LSB) при этом записывается ноль. На рис. 15.2 показан дробный формат работы модуля умножения.

Рис. 15.2. Дробный формат работы модуля умножения

В целочисленном формате (рис. 15.3) регистр P не сдвигается, прежде чем прибавиться к MR.

Рис. 15.3. Целочисленный формат

Выбор режима осуществляется установкой 4-го разряда регистра MSTAT процессора. Если этот разряд установлен в 1, то выбран целочисленный режим. В любом формате блок умножения формирует 32-разрядный результат и передает его в блок сложения/вычитания, где получается конечное значение операции, которое записывается в MR.

Регистры ввода-вывода MAC

В операциях MAC обрабатываются данные, которые поступают на порты X и Y, а результат операций выводится на шину R. Ниже приведен перечень регистров, доступных для этих портов.

Регистры для входного порта X - MX0, МХ1, AR, MR0, MR1, MR2, SR0, SR1.

Регистры для входного порта Y - MY0, MY1, MF.

Регистры для выходного порта R - MR (MR0, MR1, MR2), MF.

Входные форматы данных

Для облегчения умножения входные операнды могут находиться в любых форматах. Входные форматы определяются как часть команды и выбираются динамически при обращении к блоку умножения.

Формат: "знаковый * знаковый" - используется при умножении двух знаковых чисел простой точности или двух старших частей знаковых чисел двойной точности.

Формат: "без знака * знаковый" или "знаковый * без знака" - используется при умножении верхней части знакового числа на нижнюю часть другого или для умножения знакового числа простой точности с числом той же точности без знака.

Формат: "без знака * без знака" - используется при умножении чисел простой точности без знака или нижних частей знаковых чисел двойной точности.

Операции над регистром MR

Как показано на рис. 15.1, регистр MR разбит на три регистра: MR0 (биты 0-15), MR1 (биты 16-31) и MR2 (биты 32-39). Каждый из этих регистров может быть загружен с DMD-шины и выведен на R-шину или DMD-шину. Регистр MR2 связан с младшими восемью разрядами этих шин. Во время передачи данных MR2 на R-шину или DMD-шину происходит добавление 8 знаковых разрядов для расширения числа до 16 разрядов. Кроме того, при загрузке данных с DMD-шины в регистр MR1 регистр MR2 служит как добавление регистра MR1, и заполняется значением старшего знакового разряда MR1. Для того чтобы загрузить в регистр MR2 данные, отличные от знакового разряда MR1, необходимо загружать MR2 после загрузки MR1. Загрузка регистра MR0 не влияет на регистры MR0 и MR1.

Насыщение и переполнение MAC

После каждой операции блок сложения/вычитания генерирует сигнал переполнения MV, который подключен к регистру состояния арифметики процессора ASTAT. Бит MV устанавливается в единицу, если результат сложения выходит за границы регистров MR1/MR2 - 32 бита, т.е. если все девять старших разрядов регистра MR одновременно не нули или не единицы.

Регистр MR имеет возможность насыщения в определенном положительном или отрицательном значении, если происходит переполнение. Насыщение зависит от состояния бита MV регистра состояний арифметики ASTAT и бита MSB регистра MR2. Операцию насыщения описывает табл. 15.3.

Таблица 15.3 Описание операции насыщения

| Флаг MV | Старший разряд MR2 | Содержимое регистра MR после операции |

|---|---|---|

| 0 | 0 или 1 | Без изменений |

| 1 | 0 | 00000000 0111111111111111 1111111111111111 (положительное) |

| 1 | 1 | 11111111 1000000000000000 0000000000000000 (отрицательное) |

Насыщение в MAC является скорее командой, чем режимом, как в ALU. Она используется при завершении последовательности умножений с накоплением, таким образом, чтобы промежуточные переполнения не привели сумматор к насыщению.

Переполнение больше старшего разряда MSB недопустимо. В обратном случае знаковый разряд будет потерян, и насыщение не будет правильным. Однако, чтобы достигнуть этого состояния, требуется 255 циклов переполнения.

Округление

В сумматоре MAC можно округлять 40-разрядный результат на границе между 15-м и 16-м разрядами. Округление относится к системе команд процессора. Округленный результат направляется либо в регистр MR, либо в регистр обратной связи MF. Когда для вывода используется MF, в него записывается 16-разрядный округленный результат. Аналогично, если для вывода выбран MR, то в MR1 записываются 16 разрядов округленного результата, а в регистр MR2 результат округления, таким образом, получается 24-разрядный округленный результат.

Сумматор производит процедуру округления без смещения. Стандартный метод смещенного округления состоит в записи единицы в 15-й разряд. Этот метод вызывает положительное смещение, так как срединное значение числа, когда MR=0x8000 округляется в сторону увеличения. Сумматор устраняет это смещение, принудительно устанавливая шестнадцатый разряд в ноль, когда значение регистра MR достигает середины. При этом четные значения MR1 округляются в сторону уменьшения, а нечетные в сторону увеличения. Таким образом достигается нулевое смещение при выборе множества равномерно распределенных значений. Для наглядности сказанного выше, в табл. 15.4 приведено два примера операций округления результата.

Таблица 15.4 Примеры операций округления результата

| Операнды и операции | Регистры | ||

|---|---|---|---|

| MR2 | MR1 | MR0 | |

| Пример 1 | |||

| Неокругленное значение, где 15-й разряд равен 1 | xxxxxxxx | xxxxxxxx 00100101 | 1xxxxxxxxxxxxxxx |

| Прибавление 1 к 15-му разряду и учет переноса | 100000000 0000000 | ||

| Округленное значение | xxxxxxxx | хххххххх 00100110 | 0xxxxxxxxxxxxxxx |

| Пример 2 | |||

| Неокругленное значение, где 15-й разряд равен 1, а разряды с 0-го по 14-й равны нулю | xxxxxxxx | хххххххх 00100110 | 100000000 0000000 |

| Прибавление 1 к 15-му разряду и учет переноса | 100000000 0000000 | ||

| Неокругленное значение, где бит 16 равен 1 | xxxxxxxx | хххххххх 00100111 | 00000000 00000000 |

| Установка 16-го разряда в ноль и получение округленного значения | xxxxxxxx | хххххххх 00100110 | 00000000 00000000 |

x - произвольное значение (0 или 1).

В первом примере число не является срединным и производится его стандартное округление.

Во втором примере число имеет срединное значение, поэтому его 16-й разряд устанавливается в ноль. Алгоритм округления применяется для каждой операции округления, но становится очевидным лишь при таком наборе младших бит, который показан в примере 2.

Смещенное округление

В процессорах ADSP-2181 возможен режим смещенного округления. Этот режим выбирается путем установки 12-го бита (BIARND) регистра управления SPORT0. Если BIARND=0, то используется операция несмещенного округления, если BIARND=1, то смещенного. Примеры таких операций приведены в табл. 15.5.

Таблица 15.5 Примеры операций округления

| Значение регистра MR до округления | Результат округления со смещением | Результат округления без смещения |

|---|---|---|

| 00-0000-8000 | 00-0001-8000 | 00-0000-8000 |

| 00-0001-8000 | 00-0002-8000 | 00-0002-8000 |

| 00-0000-8001 | 00-0001-8001 | 00-0001-8001 |

| 00-0001-8001 | 00-0002-8001 | 00-0002-8001 |

| 00-0000-7FFF | 00-0000-7FFF | 00-0000-7FFF |

| 00-0001-7FFF | 00-0001-7FFF | 00-0001-7FFF |

Этот режим действует только в том случае, когда значение регистра MR0 больше 0x8000. Во всех других случаях работают обычные операции округления. Этот режим позволяет более эффективно реализовывать алгоритмы, использующие смещенное округление, например подпрограммы речевого сжатия GSM.