Глава 8. Порт IDMA

В этой главе описывается интерфейсный порт IDMA и способы загрузки и отладки программ для сигнального процессора через этот порт.

Помимо порта прямого доступа к байтовой памяти BDMA (Byte Data Memory Access), сигнальный процессор ADSP-2181 имеет порт прямого доступа к внутренней памяти процессора IDMA (Internal Data Memory Access). Он представляет собой 16-разрядный параллельный порт, через который можно читать и записывать данные памяти процессора. Порт IDMA имеет 16-разрядную мультиплексированную шину адреса/данных IAD0–IAD15, 4 сигнала управления и 1 сигнал контроля. К сигналам управления относятся: сигнал выбора порта -IS, сигнал записи адреса ячейки памяти IAL, сигнал чтения -IRD и записи -IWR данных через порт. Сигнал контроля -IACK позволяет определить готовность порта IDMA. При чтении и записи памяти через IDMA данные транслируются через буферный регистр порта IDMA. В памяти данных процессора по адресу 0x3FE0 находится регистр управления IDMA, который предназначен для хранения адреса ячейки памяти, к которой будет производиться обращение через порт IDMA. Формат этого регистра представлен в табл. 8.1.

Таблица 8.1 Формат данных регистра управления IDMA

| Разряд | Назначение |

|---|---|

| 15 | Не используется |

| 14 | Указатель типа памяти: 0=память программ (РМ) 1=память данных (DM) |

| 13–0 | Значение начального адреса памяти процессора при обмене через IDMA (от 0 до 0x3FFF) |

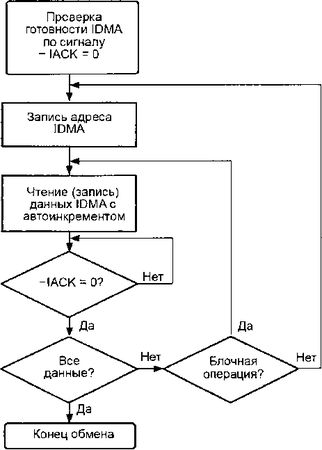

Порт IDMA имеет встроенную функцию автоинкремента (автоматического увеличения на единицу адреса памяти), что позволяет ускорить выполнение блочных операций. Кроме того, порт IDMA позволяет выполнять загрузку памяти программ процессора с автоматическим запуском программы после заполнения нулевой ячейки памяти. Протокол обращения к памяти процессора через порт IDMA достаточно прост и показан на рис. 8.1.

Рис. 8.1. Алгоритм обращения к памяти процессора

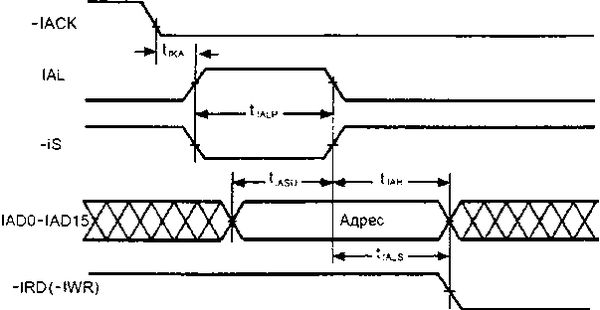

Вначале все сигналы управления портом переводятся в пассивное состояние и проверятся готовность IDMA, путем ожидания установки сигнала -IACK в логический ноль. Затем осуществляется вывод на шину IAD0–15 сигналов адреса памяти процессора, к которой будет производиться обращение. После чего формируется строб сигнала записи адреса IAL в регистр управления порта IDMA. Временная диаграмма данной операции показана на рис. 8.2, а в табл. 8.2 приведены временные параметры для этой диаграммы.

Рис. 8.2. Временная диаграмма операции защелкивания адреса IDMA

Таблица 8.2 Временные параметры диаграммы защелкивания адреса IDMA

| Параметр | Минимум |

|---|---|

| Защелкивание адреса IDMA | |

| Требуемые длительности: | |

| tIALP длительность защелкивания адреса, нс | 10 |

| tIASU установка адреса перед окончанием защелкивания, нс | 5 |

| tIAH удержание адреса после защелкивания, нс | 2 |

| tIKA-IACK=0 перед защелкиванием, нс | 0 |

| tIALS начало записи или чтения после защелкивания, нс | 3 |

Примечания:

Начало защелкивания - IS=0 и IAL=1.

Конец защелкивания - IS=1 или IAL=0.

Начало записи или чтения - IS=0 и (IWR=0 или IRD=0).

Как видно из таблицы, минимальные временные значения сигналов не превышают 10 нс, что говорит о поддержке высокой скорости операций портом IDMA. Далее производится операция чтения или записи памяти. При операции чтения данные считываются с шины IAD0–IAD15 во время активизации управляющего сигнала -IRD.

При операции записи данные выставляются на шину IAD0–IAD15, и записываются в память процессора с помощью активизации сигнала -IWR.

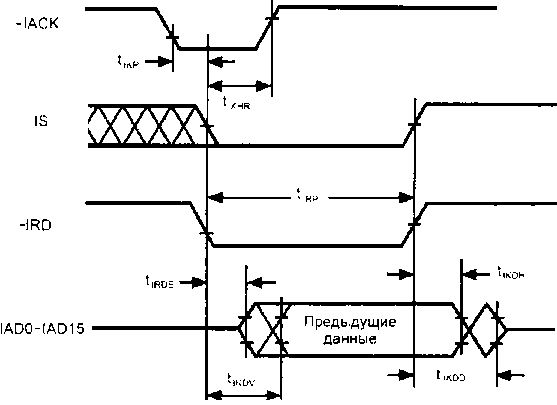

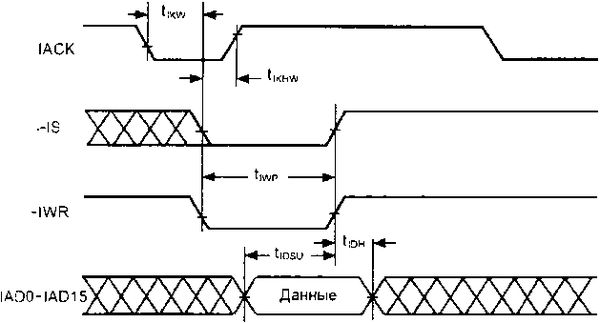

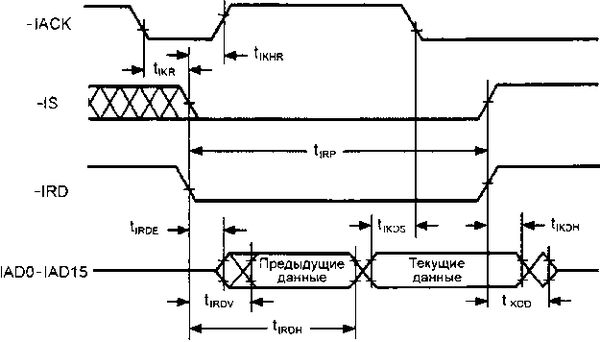

Порт IDMA поддерживает короткий (быстрый) и длинный (долгий) циклы обращения к памяти. Во время короткого цикла данные читаются и записываются без ожидания готовности порта по сигналу -IACK, используя при этом буфер порта IDMA с данными. Временные диаграммы для данных циклов обращения показаны на рис. 8.3 и 8.4 соответственно. В табл. 8.3 и 8.4 приведены характеристики сигналов для этих диаграмм.

Рис. 8.3. Временные диаграммы короткого цикла чтения через порт IDMA

Рис. 8.4. Временные диаграммы короткого цикла записи через порт IDMA

Таблица 8.3 Временные параметры диаграммы короткого цикла чтения через порт IDMA

| Параметр | Минимум | Максимум |

|---|---|---|

| Короткий цикл чтения через IDMA | ||

| Требуемые длительности: | ||

| tIKR-IACK=0 до начала чтения, нс | 0 | |

| tIRP Продолжительность сигнала чтения, нс | 15 | |

| Характеристики переключения: | ||

| tIKHR-IACK=0 после начала чтения, нс | 15 | |

| tIKDH Удержание данных после окончания чтения, нс | 0 | |

| tIKDD Сброс данных после окончания чтения, нс | 10 | |

| tIRDE Активизация предыдущих данных, нс | 0 | |

| tIRDV Достоверность предыдущих данных | 15 | |

Примечания:

Начало чтения: -IS=0 и -IRD=0.

Конец чтения: -IS=1 или -IRD=1.

Таблица 8.4 Временные параметры диаграммы короткого цикла записи через порт IDMA

| Параметр | Минимум | Максимум |

|---|---|---|

| Короткий цикл записи через IDMA | ||

| Требуемые длительности: | ||

| tIKW-IACK=0 до начала записи, нс | 0 | |

| tIWP Продолжительность записи, нс | 15 | |

| tIDSU Установка данных до окончания записи, нс | 5 | |

| tIDH Удержание данных после окончания записи, нс | 2 | |

| Характеристики переключения: | ||

| tIKHW от начала записи до -IACK=1, нс | 15 | |

Примечания:

Начало записи: -IS=0 и -IWR=0.

Конец записи: -IS=1 или -IWR=1.

Во время длинного цикла данные читаются и записываются с ожиданием готовности порта по сигналу -IACK, который активизируется только после непосредственной записи или чтения данных в памяти процессора.

Временные диаграммы для данных циклов обращения показаны на рис. 8.5 и 8.6 соответственно. В табл. 8.5 и 8.6 приведены характеристики сигналов для этих диаграмм.

Рис. 8.5. Временные диаграммы длинного цикла чтения через порт IDMA