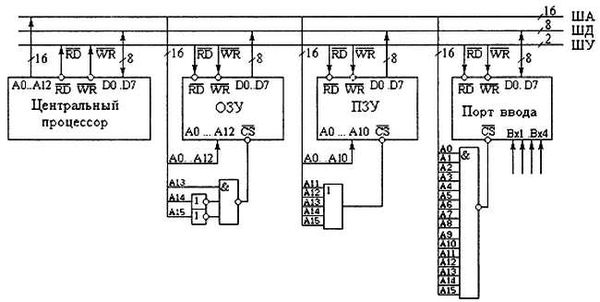

Рис. 5.1.Структурная схема простейшей микропроцессорной системы

В состав системной шины в зависимости от типа процессора входит одна или несколько шин адреса, одна или несколько шин данных и шина управления. Несколько шин данных и адреса применяются для увеличения производительности системы и используются, как правило, в сигнальных процессорах. В универсальных процессорах и контроллерах обычно применяется одна шина адреса и одна шина данных даже при реализации гарвардской структуры.

По шине данных информация передается либо к процессору, либо от процессора в зависимости от операции (записи или чтения), выполняемой микропроцессором в данный момент. В любом случае все сигналы, необходимые для работы системной шины, формируются или опрашиваются микросхемой процессора, как это рассматривалось при изучении операционного блока. То есть без микропроцессора системная шина функционировать не может. Более того, когда в микропроцессорной системе говорят об операции чтения, то предполагается, что это микропроцессор читает данные. Если в этой системе говорят об операции записи, то запись данных осуществляет именно микропроцессор.

Иногда, для увеличения скорости обработки информации, функции управления системной шины берет на себя отдельная микросхема (например, контроллер прямого доступа к памяти или сопроцессор), и тогда операции записи или чтения будет осуществлять именно эта микросхема. В современных микроконтроллерах или сигнальных процессорах эти устройства могут находиться непосредственно в составе микросхемы.

Адресное пространство микропроцессорного устройства

При подключении различных устройств к системной шине возникает вопрос - как различать эти устройства между собой? С этой целью используют индивидуальный адрес для каждого устройства, подключенного к системной шине микропроцессора. Так как адресация производится к каждой ячейке памяти устройства индивидуально, то возникает понятие адресного пространства, занимаемого каждым устройством, и адресного пространства микропроцессорного устройства в целом.

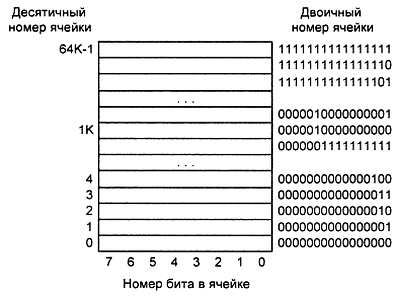

Адресное пространство микропроцессорного устройства изображается графически прямоугольником, одна из сторон которого соответствует разрядам адресуемой ячейки этого микропроцессора, а другая сторона - всему диапазону доступных адресов для этого же микропроцессора.

Обычно в качестве минимально адресуемого элемента адресного пространства выбирается 8-разрядная ячейка (байт). Диапазон доступных адресов микропроцессора определяется разрядностью шины адреса. При этом минимальный номер ячейки памяти (адрес) будет равен 0, а максимальный определяется из формулы:

M = 2 - 1

Для 16-разрядной шины это будет число 65535 (64 Кбайт). Адресное пространство этой шины приведено на рис. 5.2. Оно соответствует адресному пространству памяти микропроцессорной системы, изображенной на рис. 5.1.

Рис. 5.2.Адресное пространство микропроцессора с 16-разрядной шиной адреса

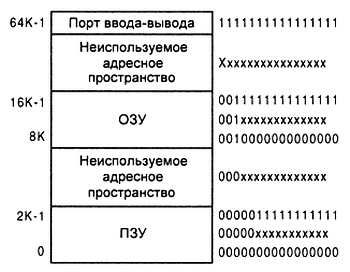

Распределением памяти называют разбиение адресного пространства на несколько областей, каждая из которых выделена для размещения ячеек какого-либо определенного элемента системы: ОЗУ, ПЗУ или внешних устройств. Часто его изображают в форме рисунка. Распределение адресного пространства, соответствующее схеме, приведенной на рис. 5.1, изображено на рис. 5.3.

Рис. 5.3.Распределение памяти микропроцессора с 16-разрядной шиной адреса

Обычно адресное пространство распределяют одновременно с проектированием принципиальной схемы устройства (созданием дешифраторов адреса для каждого подключаемого к системной шине устройства). Начнем распределение адресного пространства с выделения диапазона адресов для ПЗУ.

Микропроцессоры после включения питания и выполнения процедуры сброса всегда начинают выполнение программы с определенного адреса, чаще всего нулевого. Однако есть и исключения. Например, процессоры, на основе которых строятся универсальные компьютеры IBM PC или Macintosh, стартуют не с нулевого адреса. Программа или се загрузчик должны храниться в памяти, которая не стирается при выключении питания, т. е. в ПЗУ. Таким образом, адрес, записываемый в счетчик команд процессора после сброса, обязательно должен попадать в диапазон адресов, выделенных ПЗУ.

Выберем для построения микропроцессорной системы микросхему ПЗУ объемом 2 Кбайт, как это показано на рис. 5.1. При построении операционного блока мы договорились, что процессор после сброса начинает работу с нулевого адреса, поэтому разместим ПЗУ в адресном пространстве, начиная с нулевого адреса. Для того чтобы нулевая ячейка ПЗУ оказалась расположенной по нулевому адресу адресного пространства микропроцессора, старшие разряды шины адреса E разрядов, начиная с разряда 11) должны быть равны 0.

Так как в микросхеме ПЗУ уже имеются одиннадцать адресных выводов, то при построении схемы необходимо дополнительно декодировать старшие пять разрядов адреса (определить, чтобы они были равны 0). Это выполняется при помощи внешнего дешифратора адреса, который в данном случае вырождается в 5-входовую схему "ИЛИ". При использовании дешифратора адреса обращение микропроцессора за пределы нижней области 2 Кбайт не приведет к чтению ячеек ПЗУ, т. к. на входе выбора кристалла CS уровень напряжения останется высоким (неактивным).

Теперь подключим микросхему ОЗУ. Для примера выберем микросхему объемом 8 Кбайт. Выбор любой из ячеек этой микросхемы возможен при помощи 13-разрядного адреса, поэтому необходимо дополнительно декодировать сигналы трех старших линий 16-разрядной шины адреса. Так как начальные ячейки памяти адресного пространства уже заняты ПЗУ, то их использовать нельзя. Им соответствует значение старших разрядов адресной шины 000. Выберем для адресации ОЗУ комбинацию сигналов 001 и используем уже известные нам принципы построения схемы по произвольной таблице истинности. Дешифратор адреса выродится в данном случае в 3-входовую схему "И-НЕ" с двумя инверторами на входе. Схема дешифратора адреса ОЗУ приведена на рис. 5.1. Этот дешифратор адреса обеспечивает нулевой уровень сигнала на входе CS микросхемы ОЗУ только при комбинации старших битов адреса 001. Обратите внимание: т. к. объем ПЗУ меньше объема ОЗУ, то между областями адресов ПЗУ и ОЗУ образовалось пустое пространство неиспользуемых адресов памяти.

Так как все микропроцессоры предназначены для обработки данных, поступающих извне, то в любой микропроцессорной системе должны присутствовать порты ввода-вывода. Будем считать, что порт ввода-вывода отображается в адресное пространство микропроцессорного устройства как одиночная ячейка памяти, поэтому можно выбрать любой свободный адрес. Проще всего построить дешифратор числа FFFFh. В этом случае он превращается в обычную 16-входовую схему "И-НЕ", поэтому и выберем данный адрес для размещения порта ввода-вывода.

Способы расширения адресного пространства микропроцессора

Известно, что размер адресного пространства определяется разрядностью счетчика команд микропроцессора. Достаточно часто при развитии микропроцессорной системы возможности адресного пространства исчерпываются. В таком случае приходится прибегать к методам расширения адресного пространства.

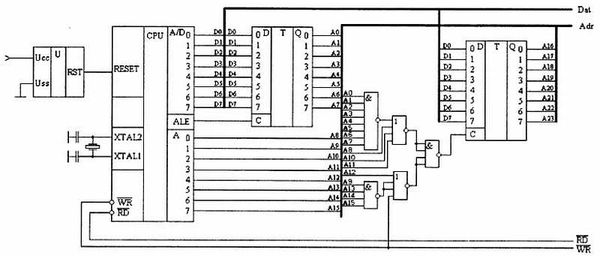

Как уже говорилось, размер адресного пространства определяется количеством адресных линий в составе адресной шины. Для увеличения адресного пространства необходимо увеличить количество этих линий (добавить старшие разряды). Сигналы на этих проводниках ничем не отличаются от сигналов, используемых для управления внешними устройствами, поэтому для расширения адресного пространства микропроцессора можно воспользоваться параллельным портом. Внешние выводы параллельного порта можно использовать в качестве старших битов адресной шины. Такой метод расширения адресного пространства называется страничным методом адресации. Регистр данных параллельного порта при использовании его для расширения адресного пространства будет называться переключателем страниц, а сам параллельный порт - диспетчером памяти. Схема использования параллельного порта в качестве переключателя страниц памяти приведена на рис. 5.4.

Рис. 5.4.Использование параллельного порта в качестве переключателя страниц памяти

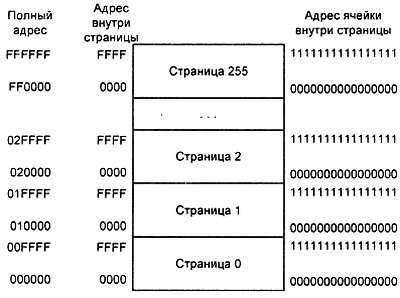

При применении 8-разрядного параллельного порта в микропроцессорной системе появились дополнительные восемь линий адреса. В результате адресное пространство микропроцессорной системы увеличилось до 16 Мбайт. Структура нового адресного пространства приведена на рис. 5.5, а принцип формирования нового адреса с использованием переключателя страниц пояснен на рис. 5.6.

Рис. 5.5.Структура страничного адресного пространства