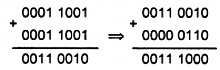

Рис. 4.15. Суммирование двух чисел 19 в двоично-десятичном коде

Представление текстовых данных в памяти процессора

Для кодирования всех символов и букв достаточно восьми двоичных разрядов. Наиболее распространенными являются таблицы кодирования текста ASCII с национальными расширениями, применяемые в DOS (и которые можно использовать для записи текстов в микропроцессорах), и таблицы ANSI, применяемые в Windows. В этих двух группах таблиц первые 128 символов совпадают. В этой части таблицы содержатся символы цифр, знаков препинания, латинские буквы верхнего и нижнего регистров и управляющие символы. Национальные расширения символьных таблиц и символы псевдографики содержатся в последних 128 кодах этих таблиц, поэтому кодировки русских текстов в DOS и Windows не совпадают. Таблица ASCII-символов приведена в Приложении.

Арифметико-логические устройства

Теперь после того как мы научились работать с двоичными кодами, можно перейти к устройствам, которые могут выполнять различные операции над этими числами - суммировать, вычитать, увеличивать и уменьшать на единицу. При этом выбор выполняемой операции желательно выполнять также при помощи двоичного кода. Такое устройство получило название арифметического устройства. Если же оно, кроме арифметических операций, выполняет еще и логические, то его называют арифметико-логическим устройством (АЛУ).

Ранее были рассмотрены схемы, осуществляющие суммирование многоразрядных кодов. Однако часто требуется осуществлять не только суммирование, но и вычитание двоичных кодов. Двоичные коды, при помощи которых можно записывать отрицательные числа, уже рассматривались в предыдущих разделах. Там же было показано, что при использовании дополнительных кодов операцию вычитания двух положительных чисел можно заменить операцией суммирования положительного и отрицательного числа, при этом получение двоичного отрицательного числа из положительного является элементарной операцией. Для этого необходимо проинвертировать число и прибавить к нему 1.

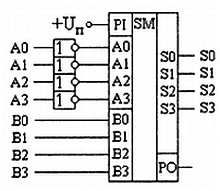

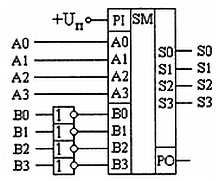

Схема вычитателя числа А из числа В приведена на рис. 4.16, а схема читателя числа В из числа А приведена на рис. 4.17. В этих схемах прибавление единицы к проинвертированному числу осуществляется подачей уровня логической единицы на вход переноса сумматора PL. Основным элементом этих двух схем является сумматор. Различаются они лишь местом включения инверторов.

Рис. 4.16.Схема вычитателя числа А из числа В

Рис. 4.17.Схема вычитателя числа В из числа А

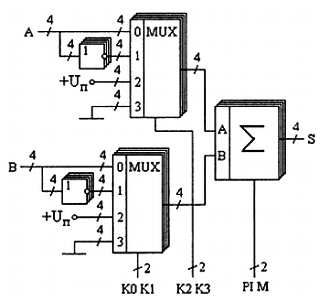

Если же потребуется в процессе вычислений изменять арифметическую операцию, то в схему можно ввести коммутатор, который будет изменять ее внутреннюю структуру в зависимости от выполняемой арифметической операции. Такое устройство получило название арифметического устройства. Его структурная схема приведена на рис. 4.18. По ней легко получить принципиальную схему, поэтому для упрощения анализа все дальнейшие рассуждения будем производить по структурной схеме.

Рис. 4.18.Структурная схема арифметического устройства

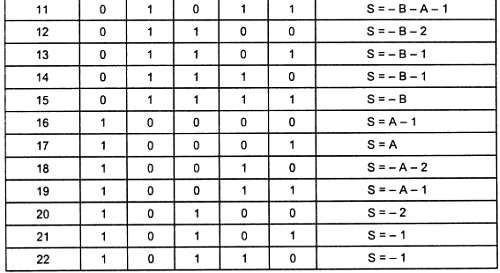

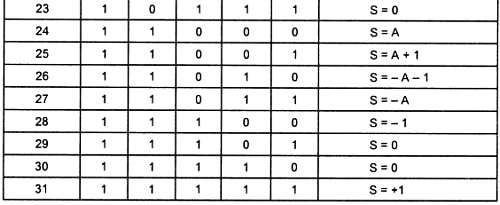

В приведенной на рис. 4.18 схеме используются четырехвходовые мультиплексоры, для управления каждым из которых достаточно двух битов. То есть для управления всей схемой в целом достаточно четырех сигналов управления. Попытаемся построить таблицу операций, которые будет выполнять эта схема. На результат операции будет влиять входной сигнал переноса сумматора PI, поэтому его тоже включим в состав кода, управляющего схемой. Операции, которые выполняются арифметическим устройством в зависимости от кода, поданного на управляющие линии, приведены в табл. 4.2.

Проанализируем эту таблицу. Если на все управляющие входы подать низкий потенциал, то к входу сумматора будут подключены коды А и В без инверсии. В этом случае будет производиться операция суммирования. Эта ситуация отображена первыми двумя строками (с номерами 0 и 1) таблицы выполняемых операций.

Операция вычитания осуществляется строками 2, 3, 8 и 9. В этом случае один из операндов поступает на вход сумматора через блок инверторов. Единица, требуемая для получения дополнительного кода, подается на вход переноса сумматора PI.

Часто используемой операцией является увеличение числа на единицу (инкрементирование) или уменьшение числа на единицу (декрементирование). Эти операции позволяют легко организовывать циклы в программе и переходить от предыдущего операнда к следующему. Они могут быть выполнены при помощи кодов, записанных в строках 4, 7, 16 и 25.

Кроме того, схема арифметического устройства может просто передавать на выход любой из входных кодов без изменения, что позволяет осуществлять копирование данных (суммирование с константой ноль) через это устройство без дополнительных схем коммутации.

При небольшом изменении схемы такое устройство сможет осуществлять не только арифметические, но и логические операции. Для этого нужно ввести дополнительный коммутатор, который будет разрывать цепи переноса между разрядами. Эта управляющая цепь обычно называется М. Подчеркнем основную особенность полученного устройства: выбор вида выполняемой операции при помощи кода, подаваемого на специальные выводы. Это дает возможность использовать одно и то же устройство для выполнения различных функций. Разработка такого устройства позволила обменивать большую скорость выполнения отдельных операций на сложность реализуемого алгоритма, что, в конце концов, привело к разработке микропроцессорных систем. Развитие этих систем изменило окружающий нас мир.

Классификация микропроцессоров

Прежде чем приступить к изучению внутреннего устройства микропроцессоров, рассмотрим основные их типы.

По внутреннему устройству в настоящее время наметилось два направления развития микропроцессоров:

- RISC-процессоры (процессоры с сокращенным набором команд);

- CISC-процессоры (процессоры с полным набором команд).

В процессорах с полным набором команд используется уровень микропрограммирования, обеспечивающий декодирование и выполнение команд микропроцессора. Команды микропрограмм называют микрокомандами. В этих процессорах формат команды не зависит от аппаратуры процессора. На одной и той же аппаратуре при смене микропрограммы могут быть реализованы различные микропроцессоры.

С другой стороны, смена аппаратуры никак не влияет на программное обеспечение микропроцессора. При разработке новых микросхем можно использовать аппаратурные решения, никак не связанные с предыдущей микросхемой. Главное, чтобы микропрограмма эмулировала эту микросхему. То есть пользователь воспринимает новую микросхему как полный аналог старой. С его точки зрения у микропроцессора только увеличивается производительность, снижается потребление энергии, уменьшаются габариты устройств.

Определение микрокоманды и пример реализации микропрограммы будут подробно рассмотрены ниже по тексту данной главы. Поэтому сейчас эти понятия уточняться не будут.

Неявным недостатком CISC-процессоров является то, что производители микросхем стараются увеличить количество команд, которые может выполнять микропроцессор, тем самым увеличивая сложность микропрограммы и замедляя выполнение каждой команды.

В RISC-процессорах декодирование и исполнение команды производятся аппаратно, поэтому количество команд ограничено минимальным набором. В этих процессорах понятия команда и микрокоманда совпадают.

Преимуществом этого типа процессоров является то, что команда может быть в принципе выполнена за один такт (не требуется выполнение микропрограммы), однако для выполнения тех же действий, которые выполняет одиночная команда CISC-процессора, требуется выполнение некоторой последовательности команд RISC-процессоров, иногда это последовательность довольно длинная. То есть выигрыш в быстродействии микропроцессора может быть сведен к нулю.