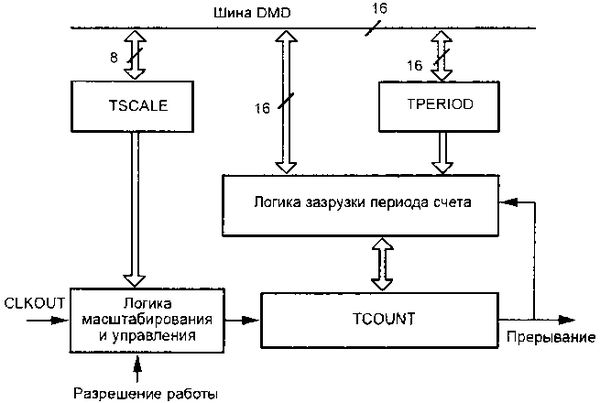

Рис. 20.1. Структурная схема таймера

Как видно из рисунка, таймер включает в себя 16-разрядный регистр периода TPERIOD, 8-разрядный регистр масштабирования TSCALE, 16-разрядный регистр-счетчик TCOUNT и логику управления. Все три регистра отображены на область памяти данных процессора в соответствии с табл. 20.1.

Таблица 20.1 Формат регистров таймера, отображенных на память данных процессора

| Разряды регистров | Адрес | |||||||

|---|---|---|---|---|---|---|---|---|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | |

| TPERIOD | 0x3FFD | |||||||

| TCOUNT | 0x3FFC | |||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0x3FFB |

| Разряды регистров | Адрес | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| TPERIOD | 0x3FFD | |||||||

| TCOUNT | 0x3FFC | |||||||

| TSCALE | 0x3FFB | |||||||

Разрешение работы таймера производится установкой в единицу 5-го разряда регистра состояния процессора MSTAT. Когда работа таймера разрешена, регистр-счетчик TCOUNT декрементируется сигналами от логики масштабирования. При достижении счетчиком нуля, формируется прерывание таймера для процессора. После чего в регистр-счетчик TCOUNT автоматически загружается значение регистра периода TPERIOD и работа таймера продолжается.

Регистр масштабирования TSCALE содержит коэффициент деления тактовой частоты процессора и позволяет изменять время между прерываниями таймера.

Значения регистров TPERIOD и TSCALE могут загружаться с шины DMD. Таким образом, с помощью таймера можно генерировать прерывания каждые (TPERIOD+1)*(TSCALE+1) циклов, т.е. от 1 до FFFFFF16=1677721510 циклов. При тактовой частоте процессора 40МГц таймер может формировать прерывания с периодом от 20 нс до 0,3 с.

При необходимости прерывания таймера можно маскировать, сбрасывать или принудительно устанавливать программным образом.

Ниже приведен пример команд инициализации таймера:

{Регистр таймера TPERIOD=0x3FFD (Регистр периода)}

AX0=0X7FFF; DM(TPERIOD)=AX0;

{Регистр таймера TCOUNT=0x3FFC (Регистр счетчика)}

AX0=0X7FFF; DM(TCOUNT)=AX0;

{Регистр таймера TSCALE=0x3FFB (Регистр масштабирования)}

AX0=255; {ОТ 0 ДО 255} DM(TSCALE)=AX0;

Строка обработки прерывания в программе может иметь следующий вид:

jump V_TIMER; nop; nop; nop; {Вектор прерывания таймера}

Следующий пример обработчика прерывания таймера позволяет автоматически наращивать значения ячейки памяти 0x3000 и выводить эти значения в порт ввода-вывода по адресу 2000.

{===== Обработчик прерывания таймера =====}

V_TIMER:

ENA SEC_REG;

AX0=DM(0X3000);

AR=AX0 + 1;

DM(0X3000)=AR;

IO(2000)=AR;

RTI;

Подобным образом можно организовывать автоматическую регенерацию динамической памяти, подключаемой к сигнальному процессору. Учитывая, что объем такого типа памяти составляет десятки миллионов байт в одной микросхеме, можно догадаться о мощности устройств, создаваемых с ее применением. В то же время регенерация динамической памяти очень легко решается при подключении ее к сигнальному процессору.

Глава 21. Синхронные последовательные порты

В этой главе говорится о двух синхронных последовательных портах, входящих в состав сигнального процессора, об их устройстве, назначении и использовании.

Кроме рассмотренных нами вычислительных и других устройств, сигнальный процессор имеет встроенные коммуникационные средства в виде двух синхронных последовательных портов, называемых SPORT0 и SPORT1. Данные порты поддерживают множество последовательных протоколов обмена данными и, кроме того, обеспечивают прямое соединение процессоров в многопроцессорной системе. Рассмотрим подробнее эти устройства и команды, которыми они управляются.

Каждый SPORT имеет пять интерфейсных линий:

SCLK - тактовый сигнал;

RFS - прием кадровых синхроимпульсов;

TFS - передача кадровых синхроимпульсов;

DR - прием данных;

DT - передача данных.

SPORT1, в отличие от SPORT0, имеет возможность программно переназначать все сигнальные линии, кроме SCLK. Описание выводов последовательных портов сигнального процессора ADSP-2181 приведено в табл. 21.1.

Таблица 21.1 Описание выводов последовательных портов сигнального процессора ADSP-2181

| Сигнал | Направление | Назначение |

|---|---|---|

| DT0 | О | Передача данных |

| TFS0 | I/O | Кадровая синхронизация передачи |

| RFS0 | I/O | Кадровая синхронизация приема |

| DR0 | I | Прием данных |

| SCLK0 | I/O | Программируемый генератор порта 0 |

| DT1/FO | O | Передача данных или выходной флаг |

| TFS1/IRQ1 | I/O | Кадровая синхронизация передачи или внешний запрос прерывания 1 |

| RFS1/IRQ0 | I/O | Кадровая синхронизация приема или внешний запрос прерывания 0 |

| DR1/FI | I | Прием данных или входной флаг |

| SCLK1 | I/O | Программируемый генератор порта 1 |

I - вход, O - выход, I/O - вход/выход.

SPORT0 и SPORT1 способны одновременно принимать последовательный поток данных на входе DR и передавать последовательный поток через выход DT, обеспечивая тем самым дуплексный режим работы. Кроме того, передаваемые и принимаемые данные могут быть аппаратно запакованы и распакованы с помощью аппаратного блока компандирования. Данная процедура широко применяется в аппаратуре цифровой связи. Биты данных синхронизируются тактовыми синхроимпульсами SCLK внутреннего генератора, если процессор запрограммирован как источник синхронизации. Если порт запрограммирован в режим внешней синхронизации, SCLK становится входом для внешних импульсов синхронизации.

Сигналы кадровой синхронизации RFS и TFS используются для указания начала слова последовательно передаваемых данных или потока последовательно передаваемых слов. Эти сигналы также могут генерироваться внутри процессора или формироваться извне.

На рис. 21.1 показана структурная схема последовательного порта.