TOGGLE FL0 {Инвертировать флаг FL0}

Met2: IDLE; {Режим ожидания прерывания}

JUMP Met2:

Таблица 18.1 Допустимые значения <term>

| Значение <term> | Пояснение |

|---|---|

| CE | Счетчик циклов пуст |

| EQ | Равно нулю |

| NE | Не равно нулю |

| LT | Меньше нуля |

| GE | Больше или равно нулю |

| LE | Меньше или равно нулю |

| GT | Больше нуля |

| АС | Перенос АЛУ |

| NOT AC | Нет переноса АЛУ |

| AV | Переполнение АЛУ |

| NOT AV | Нет переполнения АЛУ |

| MV | Переполнение умножителя |

| NOT MV | Нет переполнения умножителя |

| NEG | Входной операнд "xop" отрицателен |

| POS | Входной операнд "xop" положителен |

| FOREVER | Бесконечный цикл |

Таблица 18.2 Допустимые значения <cond>

| Значение <cond> | Пояснение |

|---|---|

| EQ | Равно нулю |

| NE | He равно нулю |

| LT | Меньше нуля |

| GE | Больше или равно нулю |

| LE | Меньше или равно нулю |

| GT | Больше нуля |

| AC | Перенос АЛУ |

| NOT AC | Нет переноса АЛУ |

| AV | Переполнение АЛУ |

| NOT AV | Нет переполнения АЛУ |

| MV | Переполнение умножителя |

| NOT MV | Нет переполнения умножителя |

| NEG | Входной операнд "xop" отрицателен |

| POS | Входной операнд "xop" положителен |

| NOT CE | Счетчик циклов не пуст |

| FLAG_IN* | Вывод FI=1 |

| NOT FLAG_IN* | Вывод FI=0 |

*Только для команд JUMP, CALL

Глава 19. Генераторы адресов

В этой главе говорится об устройствах генераторов адресов сигнального процессора и выполняемых с его помощью командах.

Ранее мы уже рассматривали назначение генераторов адресов (DAG). На этот раз рассмотрим их структуру и команды, которые они позволяют выполнять.

Сигнальный процессор имеет в своем составе два независимых генератора адреса данных, обеспечивающих одновременный доступ к памяти данных и памяти программ. Генераторы адреса осуществляют косвенную адресацию данных. Оба генератора могут выполнять автоматическую модификацию адреса данных. С помощью циклических буферов, они могут выполнять модификацию адреса по модулю. Отличие генераторов адреса друг от друга состоит в следующем. Первый генератор адреса (DAG1) генерирует только адреса памяти данных, но обеспечивает при этом изменение порядка разрядов в адресе на обратный (реверс разрядов). Второй генератор адреса (DAG2) генерирует как адреса памяти данных, так и адреса памяти программы, но не способен поддерживать реверсную адресацию.

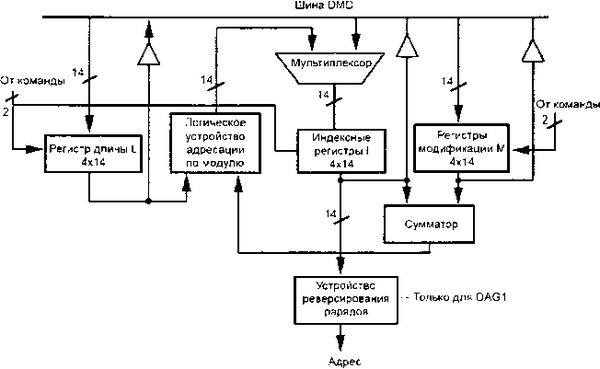

Структурная схема генератора адреса приведена на рис. 19.1. Отличия структуры DAG1 от DAG2 показаны на самой схеме.

Рис. 19.1. Структурная схема генератора адреса

Каждый генератор имеет в своем составе три регистровых блока: блок регистров модификации (M), блок индексных регистров (I) и блок регистров длины (L). Каждый из регистровых блоков состоит из четырех регистров разрядностью 14 бит. Чтение и запись данных в эти регистры осуществляется через шину данных DMD. Индексные регистры I содержат действительные адреса, используемые для доступа к памяти. При косвенной адресации данных адрес, находящийся в выбранном индексном регистре, становится адресом памяти. Разряды адреса на выходе DAG1 могут быть переставлены в обратном порядке за счет установки соответствующего бита режима в регистре состояний режима MSTAT или при помощи команды ENA BIT_REV. Реверс адреса (адресация с перестановкой разрядов в обратном порядке) необходим для выполнения операций БПФ (быстрого преобразования Фурье) для цифровых значений сигнала. Данную операцию часто называют скремблированием (от английского слова scramble - смешивать). Сброс бита режима реверса адреса в регистре состояний режима MSTAT производится командой DIS BIT_REV. Для наглядности сказанного в табл. 19.1 приведен нормальный и реверсивный порядок адресов для 2-, 3- и 4-разрядных адресов. Из таблицы видно, каким образом при этом перемешиваются значения адреса.

Таблица 19.1 Нормальный и реверсивный порядок адресов для 2-, 3- и 4-разрядных адресов

| Значение адреса | Нормальный порядок | Реверсивный порядок | Значение адреса |

|---|---|---|---|

| 2-разрядный адрес | |||

| 0 | 00 | 00 | 0 |

| 1 | 01 | 10 | 2 |

| 2 | 10 | 01 | 1 |

| 3 | 11 | 11 | 3 |

| 3-разрядный адрес | |||

| 0 | 000 | 000 | 0 |

| 1 | 001 | 100 | 4 |

| 2 | 010 | 010 | 2 |

| 3 | 011 | 110 | 6 |

| 4 | 100 | 001 | 1 |

| 5 | 101 | 101 | 5 |

| 6 | 110 | 011 | 3 |

| 7 | 111 | 111 | 7 |

| 4-разрядный адрес | |||

| 0 | 0000 | 0000 | 0 |

| 1 | 0001 | 1000 | 8 |

| 2 | 0010 | 0100 | 4 |

| 3 | 0011 | 1100 | 12 |

| 4 | 0100 | 0010 | 2 |

| 5 | 0101 | 1010 | 10 |

| 6 | 0110 | 0110 | 6 |

| 7 | 0111 | 1110 | 14 |

| 8 | 1000 | 0001 | 1 |

| 9 | 1001 | 1001 | 9 |

| 10 | 1010 | 0101 | 5 |

| 11 | 1011 | 1101 | 13 |

| 12 | 1100 | 0011 | 3 |

| 13 | 1101 | 1011 | 11 |

| 14 | 1110 | 0111 | 7 |

| 15 | 1111 | 1111 | 15 |

Генераторы адреса используют пост-модификацию. Т.е. после доступа к данным при использовании косвенной адресации содержимое заданного регистра модификации M прибавляется к содержимому индексного регистра I для формирования нового значения регистра I. Выбор регистров M и I в пределах одного DAG произволен. Т.е. любой из индексных регистров I0–I3 DAG1 может быть модифицирован содержимым любого из регистров модификации M0–M3. Для DAG2 аналогично используются регистры I4–I7 и M4–M7. Значения модификации, содержащиеся в регистрах модификации M, являются знаковыми числами, поэтому следующий вычисленный адрес может быть больше или меньше предыдущего.

Генераторы адреса поддерживают адресацию линейных и циклических буферов данных. Содержимое регистра длины L определяет режим адресации для соответствующего индексного регистра I. При адресации циклических буферов регистр L инициализируется длиной буфера. При адресации линейных буферов регистр L инициализируется нулем. Для каждого регистра I соответствующий регистр L несет информацию о длине буфера. Если сумма значений регистра модификации M и индексного регистра I превышает значение длины циклического буфера, модифицированное значение регистра I вычисляется логическим устройством адресации по модулю с использованием значения регистра длины L.

Поскольку регистры I и L содержат беззнаковые числа, два старших разряда шины данных заполняются при чтении этих регистров нулями. Регистры модификации M хранят числа со знаком, поэтому старшие два разряда шины данных дополняются знаковым расширением при их чтении.