С внешним миром процессор общается посредством четырнадцатиразрядной шины адреса EXTERNAL ADDRESS BUS, двадцати четырехразрядной шины данных EXTERNAL DATA BUS и шестнадцатиразрядной шины IDMA DMA BUS.

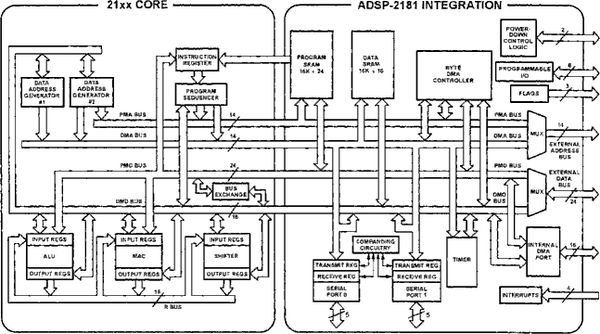

На рис. 2.2 приведена более подробная структурная схема процессора, с указанием разрядности внутренних и внешних шин и более детальным изображением всех описанных выше блоков.

Рис. 2.2. Структурная схема процессора

Более подробную структуру процессора мы рассмотрим позже, когда будем изучать его внутренние регистры и примеры программ.

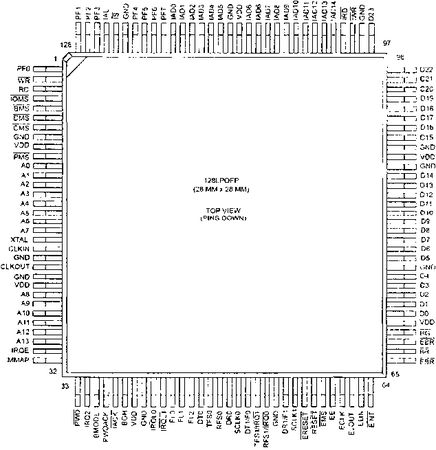

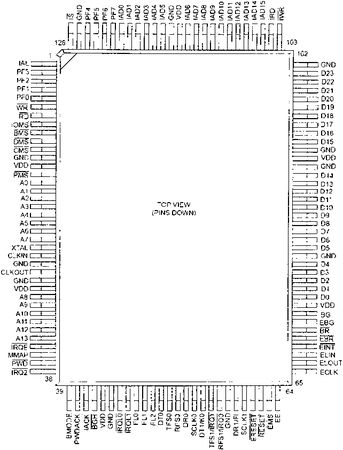

На рис. 2.3 и 2.4 представлены варианты исполнения процессора в корпусах PQFP-128 и TQFP-128, соответственно. На этих же рисунках изображено назначение всех контактов процессора и приведена их нумерация.

Рис. 2.3. Вариант исполнения процессора в корпусе PQFP-128

Рис. 2.4. Вариант исполнения процессора в корпусе TQFP-128

Изображения дают вид сверху TOP VIEW, выводами вниз PINS DOWN. Сигналы с низкими активными уровнями имеют обозначения с чертой над сигналом. Выводы двойного назначения, определяемого программированием этих выводов, обозначаются через символ "/".

В табл. 2.2 дается описание назначения выводов процессора.

Таблица 2.2 Описание выводов процессора ADSP-2181

| Наименование | Вывод I/O | Функция |

|---|---|---|

| А0…А13 | O | Адресные выводы для адресации области внешней памяти программ, памяти данных, байтовой памяти (BDMA) и устройств ввода-вывода |

| D0…D23 | I/O | Выводы данных для обмена данными с внешней памятью программ и памятью данных. Восемь старших разрядов также используются как адрес байтовой памяти. |

| -WR | O | Сигнал записи |

| -RD | O | Сигнал чтения |

| -IOMS | O | Выбор области памяти |

| -BMS | O | Выбор байтовой памяти |

| -DMS | O | Выбор памяти данных |

| -CMS | O | Выбор комбинированной памяти |

| -PMS | O | Выбор программной памяти |

| FL0, FL1, FL2 | О | Выходы-флаги |

| PF0…PF7 | I/O | Программируемые выводы |

| MMAP | I | Выбор карты памяти процессора |

| -PWD | I | Управление потреблением |

| BMODE | I | Режим загрузки 0 - ROM, 1 - IDMA |

| PWDACK | O | Контроль низкого потребления питания |

| XTAL | I | Соединение с кварцем |

| CLKIN | I | Внешний генератор, или соединение с кварцем |

| CLKOUT | O | Выходная тактовая частота |

| -RESET | I | Сброс процессора |

| -ERESET | I | Разрешение сброса |

| -IRQL0 | I | Потенциальный запрос прерывания 0 |

| -IRQL1 | I | Потенциальный запрос прерывания 1 |

| -IRQ2 | I | Динамический или потенциальный запрос прерывания 2 |

| -IRQE | I | Динамический запрос прерывания |

| -BR | I | Внешний запрос шины |

| -BG | O | Внешнее предоставление шины |

| -BGH | O | Внешнее предоставление шины, подтянутое к питанию |

| IAD0…IAD15 | I/O | Шина адреса/данных порта IDMA |

| -IACK | O | Подтверждение доступа к порту IDMA |

| -IWR | I | Вход записи в порт IDMA |

| -IRD | I | Вход чтения из порта IDMA |

| -IS | I | Вход выборки порта IDMA |

| IAL | I | Вход защелки адреса порта IDMA |

| DT0 | O | Передача данных |

| TFS0 | I/O | Кадровая синхронизация передачи |

| RFS0 | I/O | Кадровая синхронизация приема |

| DR0 | I | Прием данных |

| SCLK0 | I/O | Программируемый генератор порта 0 |

| DT1/FO | O | Передача данных, или выходной флаг |

| TFS1/IRQ1 | I/O | Кадровая синхронизация передачи, или внешний запрос прерывания 1 |

| RFS1/IRQ0 | I/O | Кадровая синхронизация приема, или внешний запрос прерывания 0 |

| DR1/FI | I | Прием данных, или входной флаг |

| SCLK1 | I/O | Программируемый генератор порта 1 |

| -EMS | Сигналы, используемые только в режиме эмуляции | |

| ЕЕ | ||

| ECLK | ||

| ELOUTELIN | ||

| EINT | ||

| -EBR | ||

| -EBG | ||

| GND | Выводы заземления | |

| VDD | Выводы питания |

Примечание: I - вход, О - выход; минус перед сигналом означает низкий активный уровень сигнала.

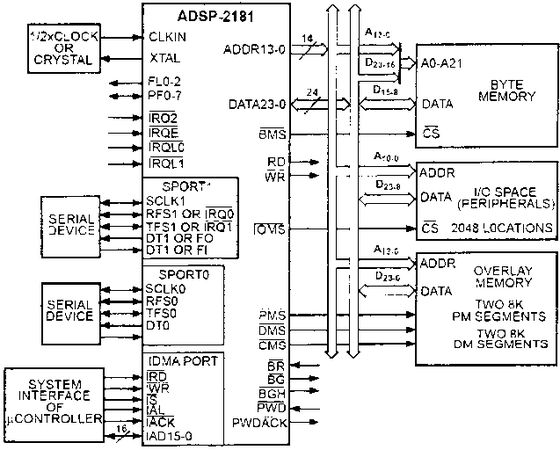

Способ подключения к процессору различных периферийных устройств показан на структурной схеме, приведенной на рис. 2.5. В качестве примера, на этой схеме показано, как подключаются следующие устройства:

Внешний генератор или кварцевый резонатор с половинной тактовой частотой процессора 1/2x CLOCK OR CRYSTAL.

Последовательные устройства SERIAL DEVICE, например кодеки.

Системный интерфейс или микроконтроллер SYSTEM INTERFACE OR MICROCONTROLLER.

Байтовая память BYTE MEMORY.

До 2048 периферийных устройств ввода-вывода I/O SPACE PERIPHERALS.

Внешняя память OVERLAY MEMORY.

Рис. 2.5. Способ подключения к процессору различных периферийных устройств

При использовании внешней памяти, допускается подключение двух 8К-словных сегмента памяти программ TWO 8К РМ SEGMENTS и двух 8К-словных сегмента памяти данных TWO 8К DM SEGMENTS.

Из схемы видно также, какие именно сигналы процессора используются для подключения всех перечисленных внешних устройств.

На рис. 2.6 показан способ подключения кварцевого резонатора к сигнальному процессору. Конденсаторы должны иметь номинальную емкость от 22 до 33 пФ, а максимальная частота кварцевого резонатора должна быть вдвое ниже максимальной внутренней частоты процессора, поскольку внутри процессора производится аппаратное умножение внешней задающей тактовой частоты. Эта удвоенная частота выводится на сигнальный вывод CLKOUT процессора. Вместо кварцевого резонатора, для формирования задающей частоты синхронизации можно использовать интегральный генератор, который, однако, несколько дороже резонатора. В этом случае выход генератора необходимо подключить к выводу CLKIN процессора, а вывод XTAL оставить неподключенным.