Часть III. Вычислительные и аппаратные устройства

В этой части книги говорится о вычислительных и аппаратных устройствах сигнального процессора, к которым относятся арифметико-логическое устройство ALU, устройство умножения MAC, устройство сдвига, устройство обмена между шинами, программный автомат, генераторы адресов, таймер и синхронные последовательные порты. Дается описание архитектуры этих устройств и выполняемых с их помощью команд.

Глава 14. Устройство АЛУ

Назначение

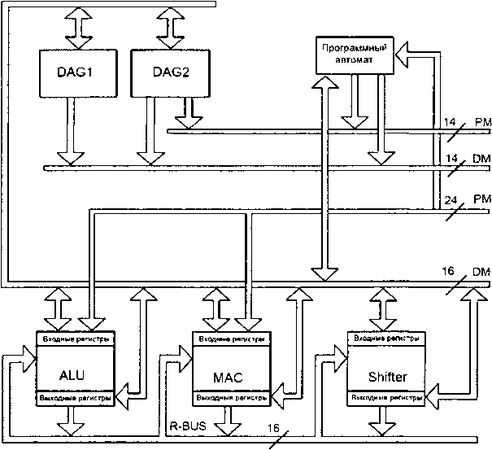

Как уже говорилось ранее, процессор ADSP-2181 содержит три независимых вычислительных устройства (рис. 14.1). К их числу относятся: арифметико-логическое устройство (ALU), умножитель с накопителем (MAC) и устройство сдвига (SHIFTER). Эти устройства работают с 16-разрядными данными и имеют аппаратную поддержку обмена данными, позволяющую обеспечить многопоточность.

Рис. 14.1. Процессор ADSP-2181

Арифметико-логическое устройство выполняет ряд стандартных арифметических и логических команд. MAC выполняет одноцикловые операции умножения, умножения-сложения и умножения-вычитания. SHIFTER осуществляет логические и арифметические сдвиги, нормализацию, денормализацию и операцию получения порядка, а также управление форматом данных, разрешая работу с плавающей точкой.

Вычислительные модули размещаются последовательно друг за другом таким образом, чтобы выход одного мог стать входом другого в следующем цикле. Результаты работы вычислительных устройств собираются на 16-разрядную шину R-BUS.

Все три устройства содержат входные и выходные регистры, которые доступны через 16-разрядную шину данных. Команды, выполняемые в устройствах, берут в качестве операндов данные, находящиеся в регистрах ввода, и после выполнения операции записывают результат в регистры вывода. Регистры являются как бы промежуточным хранилищем между памятью и вычислительной схемой. Шина R-BUS позволяет результату одного вычисления стать операндом для другой операции. Это экономит время благодаря исключению лишних пересылок данных между устройствами и памятью.

Структура устройства ALU

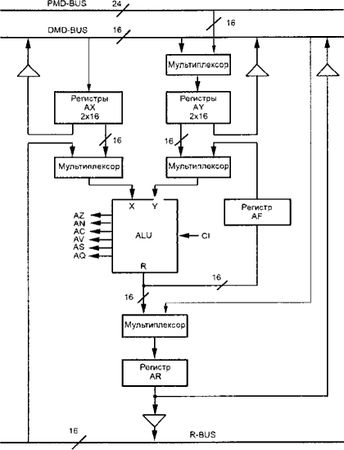

Рассмотрим подробнее ALU. Его структурная схема приведена на рис. 14.2.

Рис. 14.2. Структурная схема ALU

Арифметико-логическое устройство является 16-разрядным устройством с двумя 16-разрядными входными портами данных X и Y и одним выходным портом результата R. ALU генерирует шесть сигналов состояния: ноль (AZ), негатив (AN), перенос (AC), переполнение (AV), знак (AS) и частное (AQ). В конце каждого цикла процессора эти сигналы сохраняются в регистре состояния процессора ASTAT. Описание назначения этих сигналов состояния приведено в табл. 14.1.

Таблица 14.1 Описание назначения сигналов состояния

| Сигнал | Расшифровка | Назначение |

|---|---|---|

| AZ | ZERO (НОЛЬ) | Разряд нулевого результата. Устанавливается в 1, если результат операции равен нулю. Является результатом логического сложения всех битов регистра результатов ALU |

| AN | NEGATIV (НЕГАТИВ) | Знаковый разряд результата ALU. Устанавливается в 1, если результат отрицательный |

| AV | OVERFLOW (ПЕРЕПОЛНЕНИЕ) | Разряд переполнения. Устанавливается в 1, если происходит переполнение ALU путем переноса 1 в знаковый разряд при сложении чисел |

| AC | CARRY (ПЕРЕНОС) | Разряд переноса. Устанавливается в 1 при сложении беззнаковых чисел, если происходит переполнение ALU путем переноса 1 из старшего разряда |

| AS | SIGN (ЗНАК) | Знаковый разряд. Определяется при операции вычисления абсолютного значения числа ABS. Устанавливается в 1, если операнд имеет отрицательное значение |

| AQ | QUOTIENT (ЧАСТНОЕ) | Разряд состояния частного. Формируется только командами DIVS и DIVQ |

Порт ввода X может принимать данные от двух источников: из блока регистров АХ или с шины результата R-BUS. Шина R-BUS обеспечивает обмен данными между всеми вычислительными устройствами. Блок регистров АХ состоит из двух регистров: AX0 и AX1. Эти регистры подключены к шине памяти данных DMD-BUS. Система команд позволяет читать содержимое регистра АХ и на шину памяти программ PMD-BUS, для этого используется устройство обмена между шинами. Выводы регистров AX0 и AX1 реализованы таким образом, чтобы один из них служил операндом для ALU, а другой в это время мог считываться на шину DMD-BUS.

Порт ввода Y также принимает данные от двух источников: из блока регистров AY и регистра обратной связи AF. Блок регистров AY состоит из двух регистров AY0 и AY1. Эти регистры доступны для чтения и записи с шиной DMD-BUS. Система команд процессора позволяет читать регистры AY0 и AY1 с помощью шины PMD-BUS, но также с использованием устройства обмена между шинами. Выводы регистров AY0 и AY1 реализованы аналогично регистрам AX0 и AX1.

Выход ALU подключен к выходному регистру результата AR и через регистр обратной связи AF на вход ALU через мультиплексор. Регистр AF позволяет результату вычисления использоваться в качестве следующего операнда. Регистр AR имеет выход на шину DMD-BUS и R-BUS. В системе команд предусмотрена возможность чтения регистра AR посредством шины PMD-BUS аналогично двум предыдущим вариантам.

Любой из регистров ALU доступен для записи и чтения в течение цикла процессора (для чтения - в начале цикла, и для записи - в конце процессорного цикла). Таким образом, новое значение, записанное в конце одного цикла, может быть прочитано лишь в начале следующего. Это позволяет входным регистрам записать в ALU операнд в начале цикла и считать следующий операнд в конце того же цикла. Это также позволяет сохранить содержимое регистра результата в памяти и оперировать со следующим результатом в одном цикле.

Арифметико-логическое устройство имеет альтернативные (теневые) банки регистров AX, AY, AF и AR. На структурной схеме они изображены в виде теней. В конкретный момент времени доступен только один из типов банков. Дополнительный банк может быть использован для автоматического сохранения данных в регистрах ALU при быстром переключении на выполнение подпрограммы. В этом случае экономится время на сохранение текущих данных в памяти процессора.

Выбор главного или альтернативного банка регистров определяется битом 0 регистра режимов процессора MSTAT. Если этот разряд равен 0, то выбран главный банк, если он равен 1, то выбирается дополнительный банк.

Арифметико-логическое устройство выполняет набор стандартных арифметических и логических операций. Из арифметических операций АЛУ выполняет сложение, вычитание, отрицание, инкремент, декремент и вычисление модуля. Эти операции дополнены двумя примитивами деления, с помощью которых возможна реализация цикла многократного деления. Из логических операций АЛУ выполняет логическое сложение (OR), логическое умножение (AND), исключающее ИЛИ (XOR), и логическое отрицание (NOT). Стандартные операции ALU приведены в табл. 14.2.

Таблица 14.2 Стандартные операции ALU

| Операция | Назначение |

|---|---|

| R=X+Y | Сложение операндов X и Y |

| R=X+Y+CI | Сложение операндов X и Y с переносом |

| R=X-Y | Вычитание операнда Y из X |

| R=Y-X | Вычитание операнда X из Y |

| R=X-Y+CI-1 | Вычитание операнда Y из X с заемом |

| R=Y-X+CI-1 | Вычитание операнда X из Y с заемом |

| R= -X | Инверсия операнда X |

| R= -Y | Инверсия операнда Y |

| R=X+1 | Инкремент операнда X |

| R=Y+1 | Инкремент операнда Y |

| R=X-1 | Декремент операнда X |

| R=Y-1 | Декремент операнда Y |

| R=PASS X | Результат равен операнду X с установкой флагов регистра статуса ASTAT |

| R=PASS Y | Результат равен операнду Y с установкой флагов регистра статуса ASTAT |

| R=0 | Очистка результата |

| R=ABS X | Результат равен абсолютному значению операнда X (значение по модулю) |

| R=X AND Y | Логическое умножение операндов X и Y |

| R=X OR Y | Логическое сложение операндов X и Y |

| R=X XOR Y | Исключающее "ИЛИ" операндов X и Y |

| R=NOT X | Логическое отрицание X |

| R=NOT Y | Логическое отрицание Y |

В качестве условных записей операндов X, Y и R ALU, указанных в табл. 14.2, могут выступать следующие регистры:

- для X: AX0, АХ1, AR, MR0, MR1, MR2, SR0, SR1;

- для Y: AY0, AY1, AF;

- для R: AR и AF.

Регистры MR0, MR1, MR2 принадлежат умножителю MAC, а регистры SR0, SR1 устройству сдвига Shifter. Они доступны ALU по шине данных.

С целью обработки чисел с повышенной точностью, в ALU используются сигнал переноса CI (carry-in) и бит переноса AC (ALU carry). Операция сложения с переносом предназначена для сложения старших частей чисел, а операция вычитания с заемом - для их вычитания.