При записи в разряд порта логического 0 выходной транзистор открывается и на выводе микросхемы появляется низкий потенциал, изменить который извне невозможно. Поэтому при опросе этого вывода порта микросхемы входная информация в этом случае всегда будет восприниматься как логический 0 независимо от состояния выходов внешних устройств. Если в указанный разряд записать логическую 1, то выходной транзистор закрывается и на выводе микросхемы за счет генератора тока появляется высокий потенциал. Он может быть изменен извне на нулевой потенциал замыканием соответствующего вывода микросхемы на общий провод. В этом случае считываемое микроконтроллером значение бита будет соответствовать сигналу на выходе внешнего устройства. Поэтому перед тем как осуществить ввод информации по какому-либо выводу порта, соответствующий разряд необходимо настроить на ввод - записать в него логическую единицу.

По той же причине при настройке выводов порта на выполнение альтернативных функций в соответствующие разряды параллельного порта должны быть записаны логические I.

Кроме работы в качестве обычных портов ввода-вывода внешние выводы портов Р0-Р3 могут выполнять ряд дополнительных (альтернативных) функций.

Порт Р0 может быть использован для организации части шины адреса и шины данных при работе микроконтроллера с внешней памятью данных или программ. При этом через него из микроконтроллера выводится младший байт адреса А0-А7, а также принимается в микроконтроллер или выдается из него байт данных. Во время чтения содержимого внешней памяти во все триггеры-защелки порта Р0 аппаратно записываются 1 (т. е. содержимое порта теряется). Кроме того, через порт Р0 передаются данные при программировании внутреннего ППЗУ, и читается содержимое внутренней памяти программ при работе с программатором.

При сбросе микросхемы во все разряды порта Р0 записываются 1. У схемы Р0, в отличие от схем всех других портов, отсутствует внутренний генератор тока. Поэтому при работе с этим портом приходится подключать внешние резисторы к плюсу источника питания.

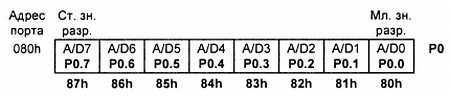

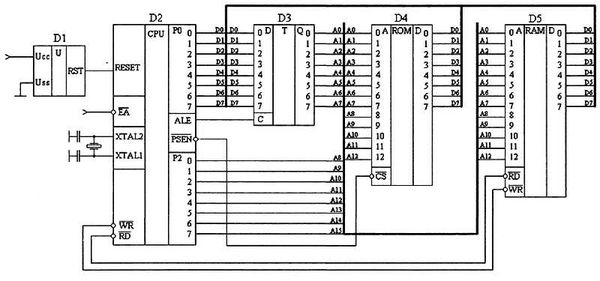

Формат и адрес порта Р0 приведены на рис. 6.5. На этом же рисунке приведены адреса отдельных битов порта Р0 в битовом пространстве. На рис. 6.6 приведена схема использования выводов портов Р0 и Р2 для подключения внешней памяти программ и внешней памяти данных.

Рис. 6.5.Формат параллельного порта Р0

Рис. 6.6. Использование выводов портов Р0 и Р2 для подключения внешней памяти программ и внешней памяти данных

Порт Р1 может быть использован для чтения внутренней памяти программ или для передачи младшего байта адреса при программировании внутреннего РПЗУ. В младших моделях микроконтроллера семейства других альтернативных функций у порта Р1 нет. При сбросе микросхемы во все разряды порта записываются 1.

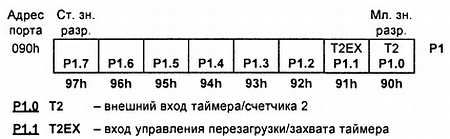

Формат и адрес порта Р1 приведены на рис. 6.7. На этом же рисунке приведены адреса отдельных битов порта Р1 в битовом пространстве.

Рис. 6.7.Формат параллельного порта Р1

Заметим, что этот порт в самых младших моделях микроконтроллеров альтернативных функций не имеет, а приведенные альтернативные функции относятся к микроконтроллерам с ядром MCS-52. Линии порта Р1 могут выполнять альтернативные функции только в том случае, если в соответствующие этим линиям разряды регистра записаны логические 1, иначе на линиях порта будет присутствовать логический 0 независимо от характера принимаемой или передаваемой информации.

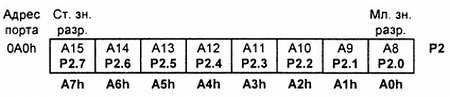

Порт Р2 может быть использован для передачи старшего байта адреса при программировании внутреннего ППЗУ и при чтении внутренней памяти программ. Через порт Р2 выводится старший байт адреса А8-А15 при работе с внешней памятью программ и внешней памятью данных (с 16-разрядным адресом). Во время доступа к внешней памяти содержимое регистра-защелки порта Р2 не изменяется. При сбросе микросхемы во все разряды порта записываются 1. Формат и адрес порта Р2 приведены на рис. 6.8. На рис. 6.6 приведена схема использования порта Р2 при подключении внешней памяти программ и внешней памяти данных.

Рис. 6.8.Формат параллельного порта Р2

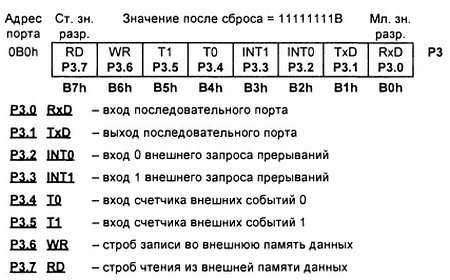

Порт РЗ. Каждая линия порта РЗ имеет индивидуальную альтернативную функцию, которая может быть задействована простым обращением к устройству, соединенному с выводом порта. Например, для того чтобы был выработан строб WR, достаточно обратиться с внешней памяти командой MOVX @DPTR, A или MOVX @R0, A. Линии порта РЗ могут выполнять альтернативные функции только в том случае, если в соответствующие этим линиям разряды регистра записаны логические 1, иначе на линиях порта будет присутствовать логический 0 независимо от характера принимаемой или передаваемой информации. При сбросе микросхемы во все разряды порта записываются 1. Формат и адрес порта РЗ приведены на рис. 6.9.

Рис. 6.9.Формат параллельного порта РЗ

Особенности построения памяти микроконтроллеров семейства MCS-51

Микроконтроллеры семейства MCS-51 построены по гарвардской архитектуре. Это означает, что память данных и память программ в этих микросхемах разделены и имеют отдельные адресные пространства. В этих микроконтроллерах имеется три адресных пространства: памяти программ, внешней памяти данных и внутренней памяти. Такое построение памяти позволяет удвоить доступное адресное пространство внешней памяти. Кроме того, построение памяти по гарвардской структуре позволяет в ряде случаев увеличить быстродействие микросхем. Для микроконтроллеров особенно важным является то обстоятельство, что не существует команд, способных осуществить запись данных в память программ и тем самым испортить управляющую программу.

Схема подключения внешних микросхем памяти к микроконтроллерам семейства MCS-51 приведена на рис. 6.6. Регистр адреса D3 на этой схеме предназначен для запоминания младших восьми битов адреса, передаваемых через шину данных/адреса, совмещенную с портом Р0. Старшие 8 битов адреса передаются через шину адреса, совмещенную с портом Р2.

Во время передачи адреса через порт Р0О микроконтроллер вырабатывает синхроимпульс на выводе ALE. Именно этот импульс позволяет запомнить младший байт адреса в регистре D3 и тем самым организовать 16-разрядную шину адреса внешней памяти.

При обращении к памяти данных и к памяти программ используются одни и те же шина адреса и шина данных, но разные управляющие сигналы. Для чтения памяти программ вырабатывается сигнал PSEN, а для чтения памяти данных - сигнал RD. Для записи информации в память данных вырабатывается сигнал WR. Именно эти управляющие сигналы и разделяют память микроконтроллера на память программ и память данных. То есть память программ доступна только для чтения, а память данных доступна и для чтения, и для записи любой информации, записанной в двоичном коде.